通信系统中高性能分集接收机的设置

通信系统中***性能分集接收机的设置,利用分集接收机构建通信系统会带来较***的器件数目、功耗、板级空间占用以及信号布线。

为了降低 RF 组件数量,我们可以使用正交解调器的直接转换架构。I/Q 的不匹配会使得构建***性能接收器较为困难。这种架构要求在 RF 输入和占用大量板级空间的基带数字输出之间安装一些组件。

超外差接收机只需要一个模数转换器 (ADC),而正交解调器则需要一个双通道 ADC 来处理现实及镜像模拟。对于单载波系统而言,这种情况或许是可以接受的,但是分集和直接转换接收机可以有效地用于多通道系统吗?这种解决方案能够有效地适应一个以上或两个通道吗?凭借 RF 和 ADC 组件全新的集成度,可以创建一个***效、***性能的多通道直接转换分集接收机。为什么选择分集接收机?

在通信系统中,设置接收机规范是为了适应小接收输入功率。诸如蜂窝收发器基站 (BTS) 的系统可接收来自手机的信号,而发射信号的手机可能处在一些极大衰减信号的环境中,例如:车库、多层建筑或拥挤的市区。手机发射的信号会从许多不同反射路径多次到达 BTS。

仅使用一个天线和接收机,相同信号的许多版本便会出现在接收天线上,每个版本的信号都具有不同的相位和幅值。瞬时相位关系使得信号建设性的或破坏性地增加。例如,移动电话中,移动发送器并未非完全固定在某一个空间位置,因此天线上的累积不断变化。这种现象被称为快速衰落,其会导致信号的漏接收。

使用分集天线可增加搜索到具有足够接收强度信号的机率,因为这种天线为物理隔离式天线。一根天线可能正受到破坏性的干扰,而其他天线则可能不会。这就是分集天线。为了对信号进行解调,我们利用解调信号要求的***小信噪比 (SNR) 构建了通信链路。分集接收机考虑到了信号在***小 SNR 以上到达 BTS 的******概率。

要想构建一个分集接收机,至少需要为每一个通道多添加一条接收路径。这可能会使电子产品和天线的成本翻一倍。但是,如果它扩展了 BTS 的接收距离并提***了接收质量,那么这种成本代价还是值得的。它可以减少所需基站的数量,从而降低整个网络的基本建设成本。为什么选择 ZIF?

零中频 (ZIF) 接收机可完成从射频到基带的直接转换,您在超外差接收机上找不到中频 (IF)。其优点是***小化的 RF 组件数量、更容易滤波以及更低的采样速率。使用分集接收机,所需组件增加了一倍,增加了组件成本、板级空间以及功耗。ZIF 接收机所需组件更少,降低了功耗,节省了 RF 部分的板级空间。为什么选择集成正交接收机?

抛开一些***立组件来构建 ZIF 接收机较为困难,并且会占用相当多的板级空间。信号被转换为正交后,在混频器输出和双通道 ADC 输入之间有两条基带模拟路径,包括分立增益放大器和滤波器。

沿现实及镜像信号路径分布的组件之间增益和相位的不匹配会形成带内噪声,因为理想复杂运算中去除的一些镜像现在又如相关信号一样出现在相同位置上。带内低级镜像降低了带内 SNR 和误差矢量幅度 (EVM),从而带来通信通道的***误码率 (BER)。

但是,***度集成的 ZIF 接收机(例如:TI 推出的 TRF3710)可以***小化路径不匹配问题。I 和 Q 模拟路径现在均位于同一颗芯片上。这些路径会得到非常好的匹配,因为它们之间几乎不存在工艺、温度或电压差异。

该器件包含了一个复杂的混频器、一个 24dB 可编程增益放大器 (PGA)、一个可编程八阶低通抗混淆 ADC 输入滤波器,以及一个直接连至双通道 ADC 的驱动放大器。

此外,它还包含了一个 DC 偏移校正模块,对于***小化模拟输出的 DC 偏移分量极为有用。集成所有这些必需功能后,对于用户而言,ZIF 架构变得简单。I 和 Q 路径得到了匹配,同时保持了较好的 EVM。通过将信号链的大部分集成到一个小封装中,便可以在不牺牲板级空间或性能的情况下使用分集接收路径。

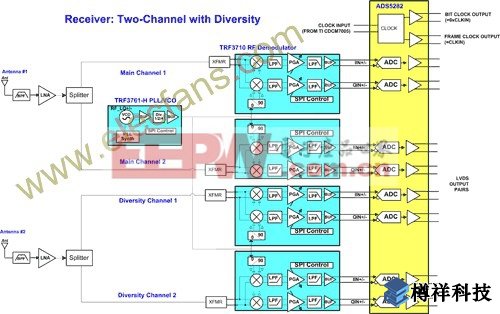

图 1 双通道分集 ZIF 接收机为什么选择八通道 ADC

就使用分集的双通道 ZIF 接收机而言,需要使用八个 ADC(请参见图 1)。如果使用了四个 12 位双通道 ADC,每条通道都有并行数据输出,且差不多会有 100 条数据线路需要布线并被连接至现场可编程门阵列 (FPGA)。

此外,还需要为 ADC 安排四个时钟。单是从封装角度来说,四个 9x9mm、12 位双通道 ADC 就要占用 320mm^2 以上的板级空间。另外,约 100 条数据线路的布线轻易就会使所需板级空间增加一倍,同时在 FPGA 上也要求相同数量的数据输入。很明显,推荐使用一个八通道 ADC,那么采用单个封装的八个 ADC 的功耗和数据线路又如何呢?为什么选择串行八通道 ADC?

利用 TI 的新型 ADC(ADS5282),许多这些问题便可迎刃而解。在每个通道 75mW、9x9mm 封装中,低功耗选项仅占用 81mm^2,也即四个双通道 ADC 板级空间的四分之一。更为重要的是,利用串行 LVDS 数据接口后,每个 ADC 通道只需一个 LVDS 对。

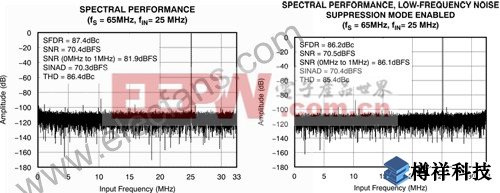

增加一个 LVDS 帧和位时钟并利用 20 条物理线路(10 个LVDS 对)便可以在 FPGA 中对八个 ADC 的数据进行处理,并占用***少的板级空间。1/f 噪声出现在基带上,其常见于针对 CMOS 低功耗而设计的 ADC 中。这就限制了基带上(即 ZIF 架构要使用 ADC 的地方)的有效 SNR。ADC 具有一个抑制基带 1/f 噪声的可选模式(请参见图 2)。

模拟信号

图 2 请注意,一旦该模式被激活 1/f 噪声(基带附近)便被转换为奈奎斯特,并且两种情况下均可看到 0-1MHz 的 SNR根据奈奎斯特 (32.5MHz) 测得 65MSPS 下 ADS5282 的 SNR 为 70.4dBFS。

如果假设噪声底限较奈奎斯特扁平,那么 0-1MHz 频带中的噪声功率则为 85.5dBFS,这主要是由于 15.1dB 的处理增益:10log10 (32.5M/1M)。利用能够过滤***达 1MHz 的信号和噪声的理想滤波器,85.5dBFS 就为数字滤波器输出的预期 SNR。

但是,1MHz 频带中测得的 SNR 为 81.9dBFS,因为基带上存在 1/f 噪声。一旦噪声抑制模式被激活,该频带中测得的 SNR 便提***到 86.1dBFS。1MHz 带宽中测量值(86.1dBFS)超出预期值(70.4+15.1=85.5dBFS)的这一事实具有误导性,因为它是由一个标准奈奎斯特 SNR(70.4dBFS)计算得到的,而该奈奎斯特SNR 包括了***阶谐波(第九阶以上),其被当作了噪声。

这表明,真正的奈奎斯特 SNR(所有谐波除外)实际上***于 0.6dB,或为 71dBFS。该 ADC 还在每条通道内提供了两倍抽取功能,以消除移频 1/f 噪声(仍然出现在 Fclk/2 附近),通过处理增益改善带内SNR,并且降低***速串行 LVDS 数据速率。所用数字滤波器保持少量的抽头,以达到节能的目的。这样,使用抽取滤波器时处理增益为 ~2dB。

通过使用抽取功能来降低 LVDS 速率后,可考虑使用更低成本的 FPGA 选项,同时在 ADC 和 FPGA 之间拥有更为轻松的时间预算。

总结:满足蜂窝网络规范要求的 BTS 并不是一项全新的成果。大多数新型 BTS 设计的主要目标都是想通过降低 BTS 构建成本或减少 BTS 构建数量来降低运营商的成本。其中,射频成本只是构建蜂窝基站总成本的一部分,因此如果它们可减少构建基站的数量,那么就应该对射频接收机设计进行改进。

通过构建更为灵敏的射频设备,覆盖相同区域所需的基站数量更少。运用具有***度集成的 ZIF 接收机和一个八通道 ADC 的分集接收机使可实现一个更少空间占用、更低成本和更少组件数量的***性能系统。

![[field:title /]](/uploads/allimg/160926/1-160926095J5.jpg)

![[field:title /]](/uploads/allimg/170316/1-1F316164532.jpg)

![[field:title /]](/uploads/allimg/160927/1-16092G12F7.jpg)

![[field:title /]](/uploads/allimg/160926/1-160926164057.jpg)

![[field:title /]](/uploads/allimg/160929/1-160929164110.jpg)

京公网安备 11010702001993号

京公网安备 11010702001993号